파트 A: 빠른 시작 – 첫 번째 OFET 시뮬레이션

이 절에서는 유기 전계 효과 트랜지스터(OFET)의 기본 이론을 소개한 뒤, OghmaNano를 사용한 시뮬레이션으로 안내합니다..

1. p형 유기 전계 효과 트랜지스터(OFET)의 기본 이론

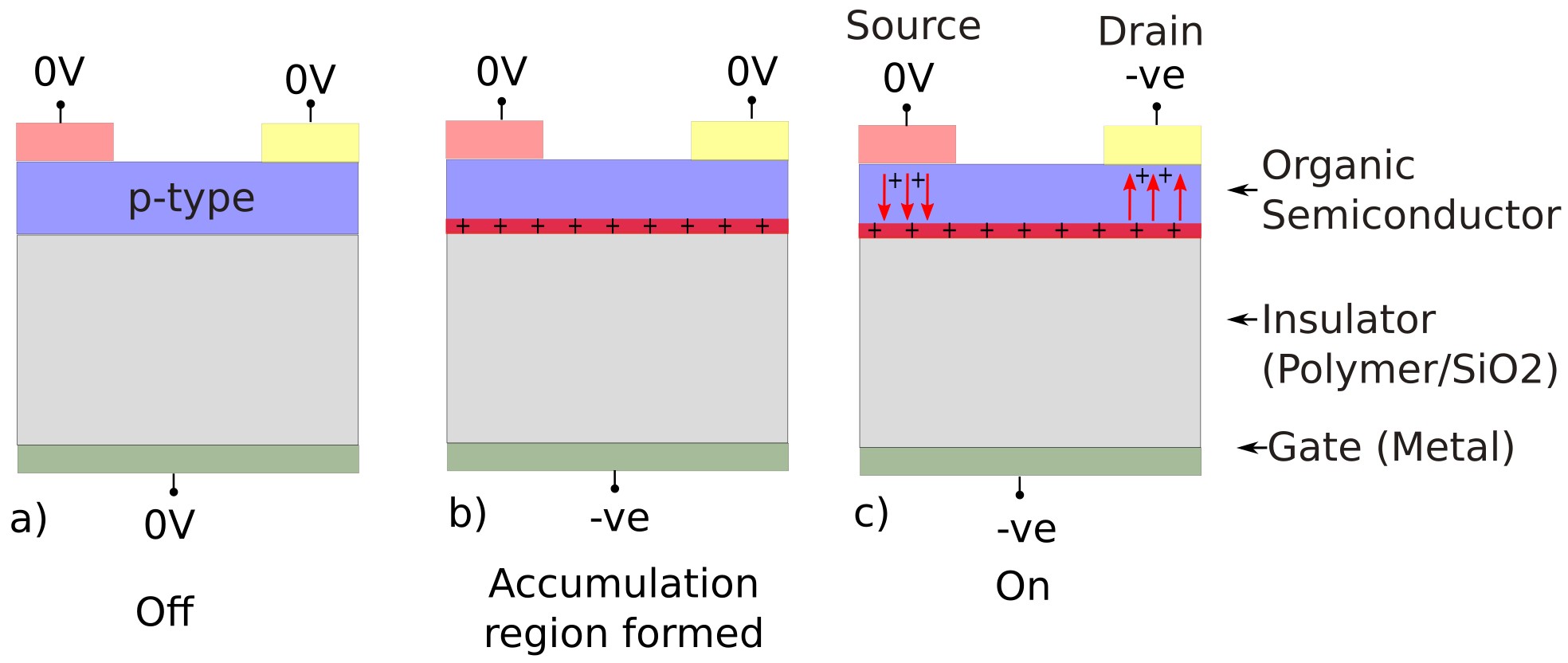

??는 전형적인 OFET의 구조를 보여줍니다. 얇은 유기 반도체 층(파란색)은 절연성 고분자/SiO2 층(회색) 위에 증착됩니다. Source와 Drain이라는 두 접촉은 반도체 상부에 위치하여 전하 운반자를 주입하고 수집하며, 세 번째 접촉인 Gate(녹색)는 절연체 아래에 위치하여 소자 동작을 제어합니다.

동작 시 Gate 전극은 유기 반도체 층을 통해 Source와 Drain 사이의 전하 운반자 흐름을 변조합니다. Gate에 전압을 인가하면 절연체를 가로지르는 전기장이 생성되고, 이로 인해 반도체-절연체 계면에 얇은 전하 층이 형성됩니다(빨간색). 이는 축전기에 전위를 인가했을 때 생기는 전하 층과 매우 유사합니다. 재료계에 따라 지배적인 운반자는 정공(p형) 또는 전자(n형)일 수 있으며, p형 재료에서는 정공 층을 형성하기 위해 -ve 전위가 인가됩니다(이는 ??b:에서 볼 수 있습니다). Source와 Drain 사이에 바이어스가 인가되면 이러한 운반자는 유도된 채널을 통해 드리프트하고 소자가 켜집니다(??c). Gate에 인가된 전압이 꺼지면 전하 채널이 사라지고 Source와 Drain 사이의 전하 운반자 흐름이 멈춥니다. 일반적으로 전류 수준은 Gate 전압에 의해 지배됩니다. 특정 임계값 이하에서는 채널이 절연 상태를 유지하고, 그 이상에서는 Gate 바이어스와 함께 채널 전도도가 증가합니다. 이러한 전계 효과 제어를 통해 OFET는 스위치로 또는 선형 영역에서는 증폭기로 동작할 수 있으며, 성능은 운반자 이동도, 임계 전압, 접촉 저항과 같은 요인에 의해 결정됩니다.

OFET의 동작은 ??a–c에 설명되어 있습니다:

- 초기 상태 — 꺼짐 (??a). 모든 단자가 0 V일 때, 반도체–절연체 계면에 유도되는 전하는 없습니다. Source와 Drain 사이에 전도 경로가 없으므로 소자는 꺼진 상태를 유지합니다.

-

Gate 바이어스 - 채널 형성 (??b).

Gate에 음의 전압을 인가하면 절연체를 가로지르는 전기장이 생성됩니다.

이 전기장은 반도체–절연체 계면으로 정공을 정전기적으로 끌어당겨

얇은 축적층(채널)을 형성합니다.

VDS=0에서는 소자에 여전히 전류가 흐르지 않지만, 전도성 채널은 형성됩니다. -

Drain 바이어스 - 전류 흐름 (??c).

Source에 대해 음의 Drain 전압을 인가하면

(

VDS<0, Source ≈ 0 V) 정공이 Source에서 채널로 주입됩니다. 정공은 Gate에 의해 유도된 채널을 따라 Drain 쪽으로 드리프트하여 Drain 전류를 생성합니다. 더 음의 Gate 바이어스는 축적 채널을 강화하고 전류를 증가시킵니다.

본질적으로 gate의 전기장은 반도체–절연체 계면에 전도성 채널을 유도합니다. Source와 Drain 사이에는 이 채널이 존재할 때만 전류가 흐르므로, OFET는 전압 제어 스위치 또는 증폭기로 동작할 수 있습니다. Gate 바이어스를 제거하면 채널이 고갈되어 소자가 꺼집니다.

위 설명은 정공이 다수 운반자인 p형 OFET를 보여줍니다. OFET는 전자가 전도 채널을 형성하는 n형 소자(+ve 전압이 gate에 인가됨) 또는 인가된 바이어스에 따라 정공과 전자를 모두 수송할 수 있는 양극성 소자로도 동작할 수 있습니다. 세 가지 모드가 모두 가능하지만, p형 OFET가 가장 일반적입니다. 이는 유기 반도체에서 정공 수송이 일반적으로 주변 조건에서 더 안정적이고 실험적으로 구현하기 더 쉽기 때문입니다.

2. 빠른 시작 OFET 시뮬레이션

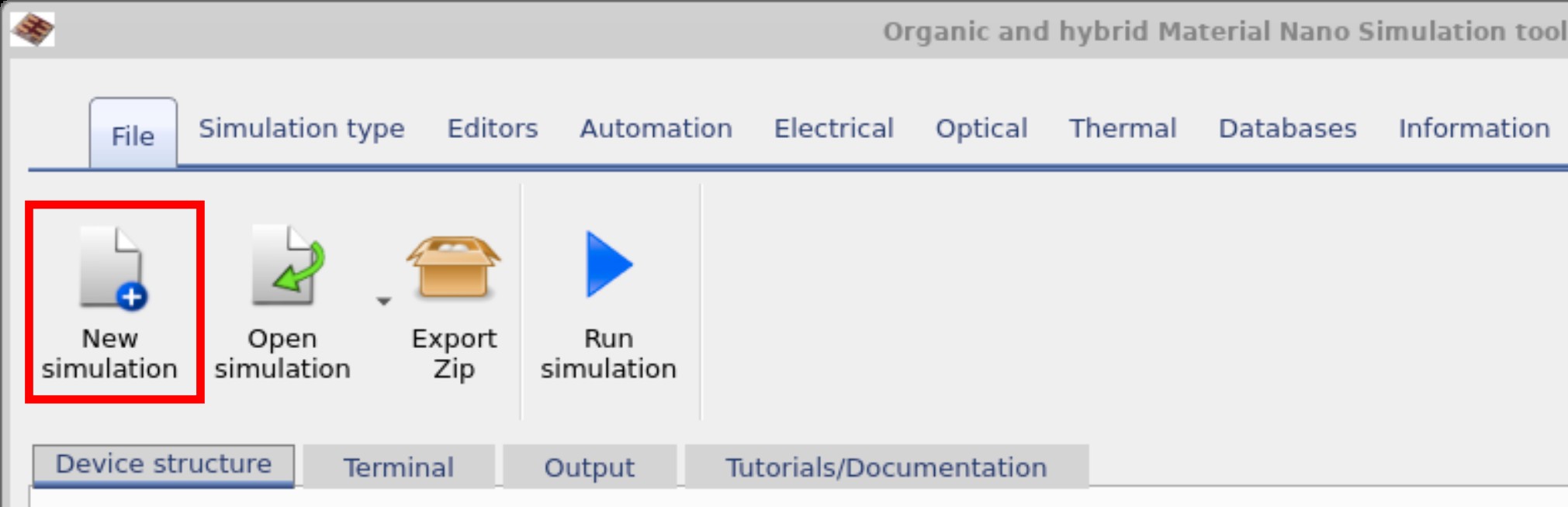

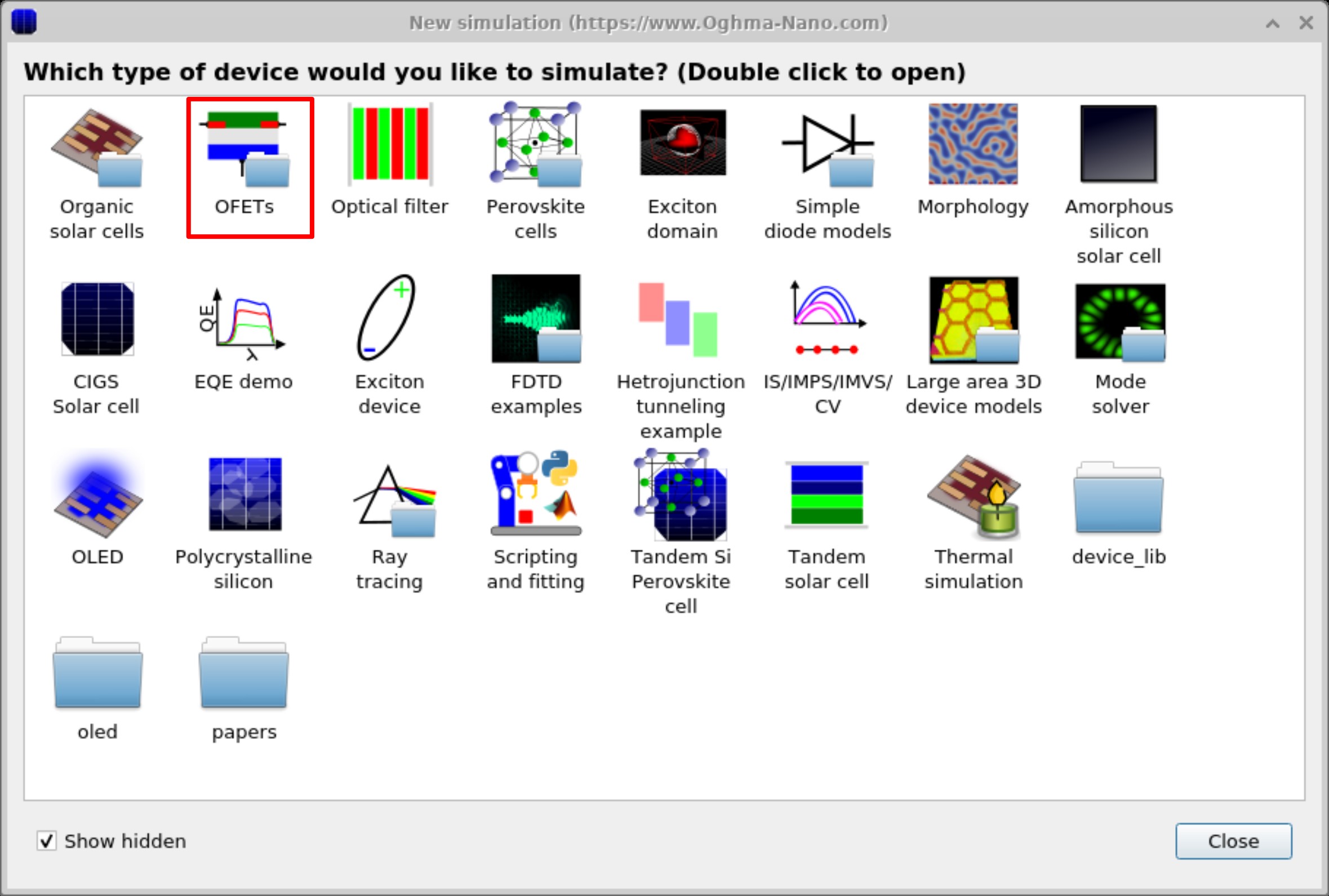

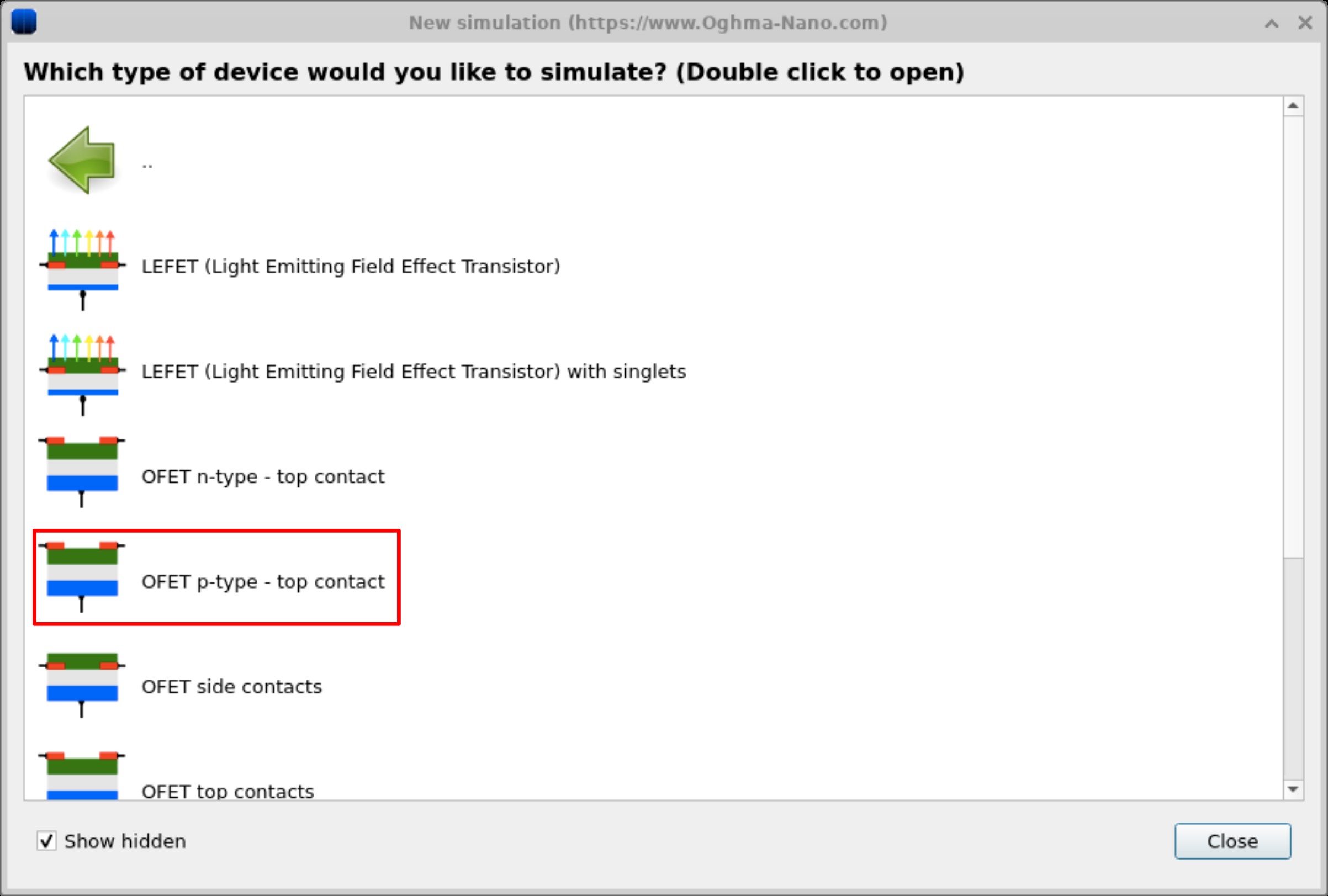

이 튜토리얼에서는 상부 접촉을 가진 p형 MOSFET에 초점을 맞춥니다. p형 반도체는 일반적으로 더 높은 정공 이동도를 보이기 때문에 유기 전자 소자에서 가장 널리 사용됩니다. 새 OFET 시뮬레이션을 만들려면 OghmaNano 기본 창의 New simulation 버튼을 클릭합니다(??). 그런 다음 새 시뮬레이션 창에서 OFET simulations를 더블 클릭합니다(그림 ?? 참조). 그러면 OFET 하위 메뉴가 나타나며, 여기에는 다른 유형의 OFET도 저장되어 있습니다. 이 예에서는 "OFET p-type top contact"를 살펴보겠습니다(??). 이것을 더블 클릭하고 새 시뮬레이션을 디스크에 저장합니다.

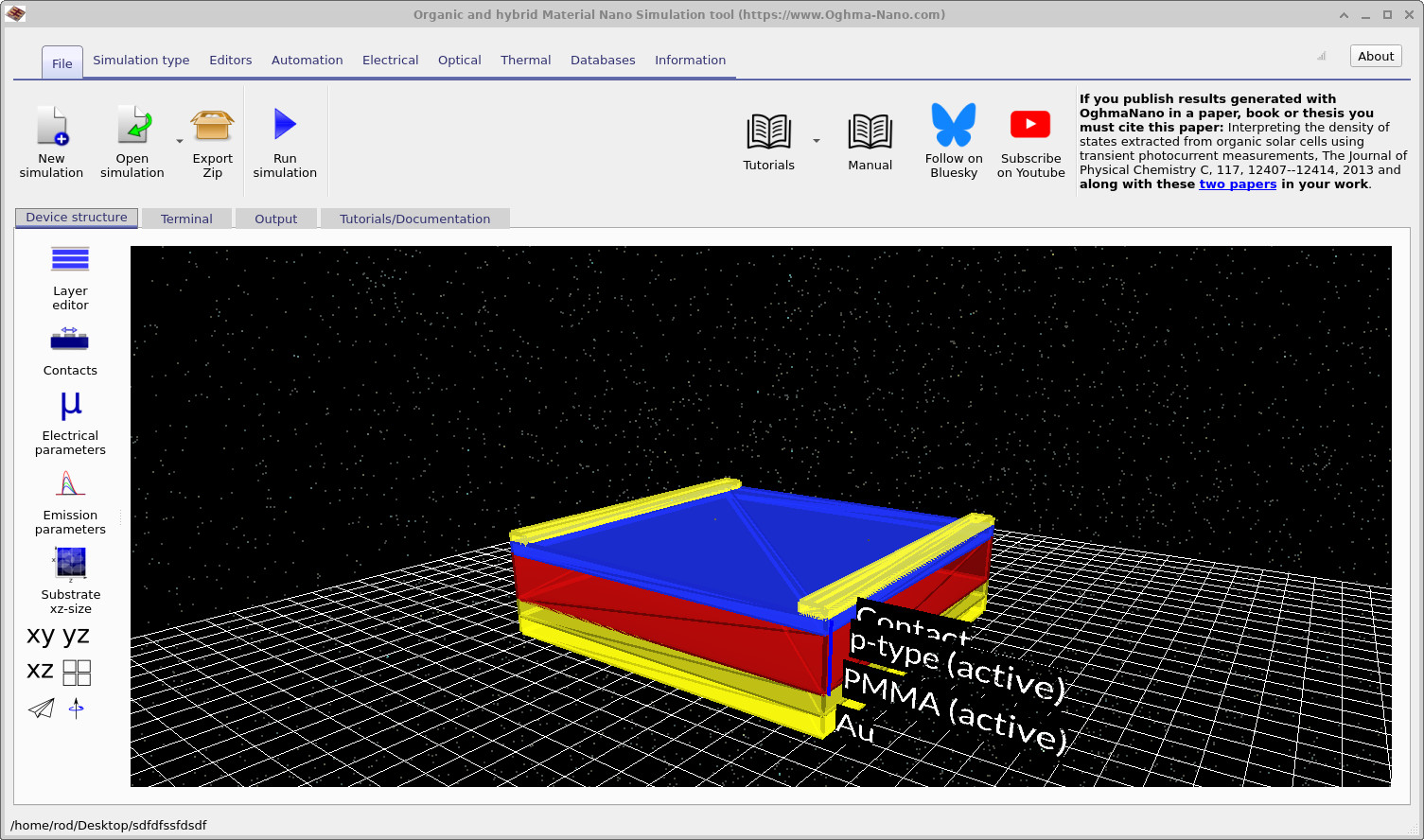

새 시뮬레이션 창을 저장하면 ??와 같은 창이 나타나야 합니다. 검은 배경에서 마우스 왼쪽 버튼을 클릭한 상태로 끌어 시뮬레이션 창을 회전시키고 3D에서 소자를 확인하십시오. 소자에는 gate, source, drain의 세 접촉이 있음을 볼 수 있습니다. source와 drain은 시뮬레이션 상단에 금색 막대로 표시되고, 반도체 층은 파란색, 절연층은 빨간색으로 표시됩니다. gate 접촉은 구조의 하단에 보입니다.

3. 첫 번째 OFET 시뮬레이션 실행

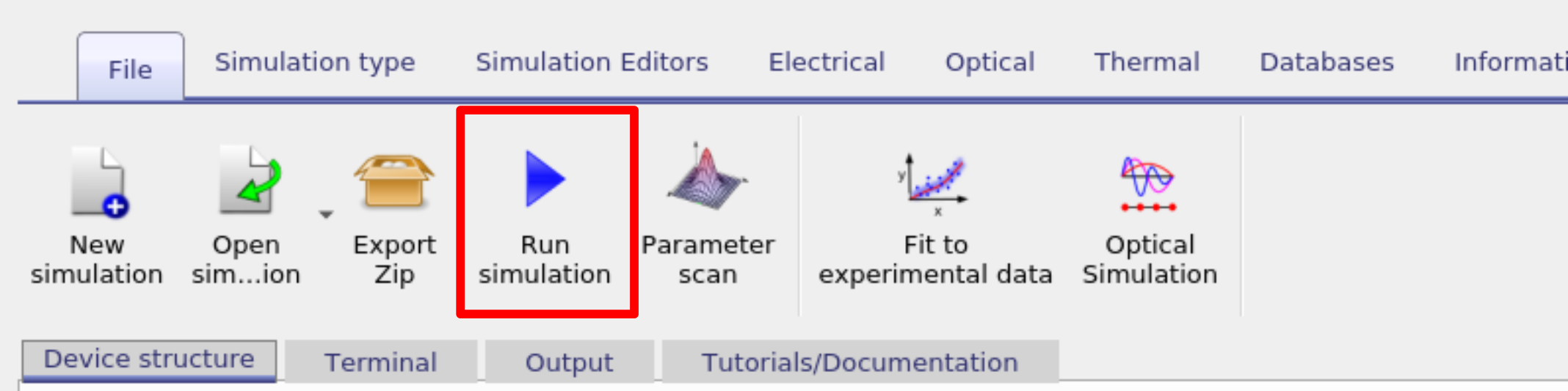

시뮬레이션을 시작하려면 Play 버튼을 클릭합니다. 1D 시뮬레이션과 비교하면 2D 시뮬레이션은 일반적으로 더 오래 걸리는데, 이는 해석기가 더 많은 메시 포인트를 가진 메시를 처리해야 하기 때문입니다. 트랩이 활성화되어 있으면 캐리어 포획/탈출 방정식도 모든 메시 포인트에서 풀어야 하므로 계산 부하가 더욱 증가합니다. 일반적으로 문제의 차원이 증가하면 실행 시간과 메모리 요구량이 빠르게 증가합니다.

jv_contact_0.csv, jv_contact_1.csv, jv_contact_2.csv), 여기에

charge.csv, device.csv, sim_info.dat와 같은

요약 및 진단 파일이 함께 생성됩니다.

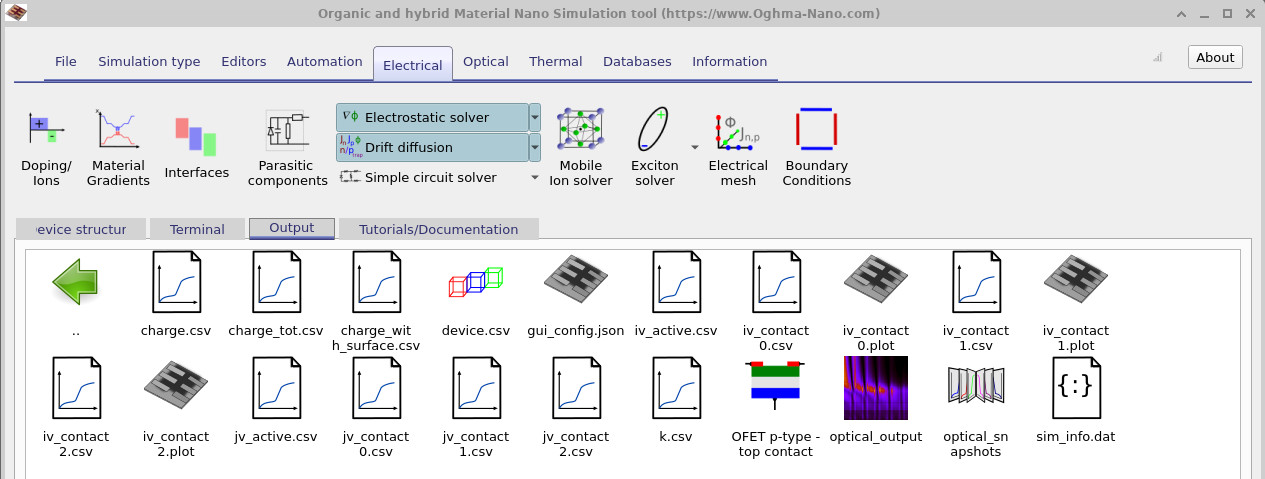

시뮬레이션이 끝나면 Output 탭을 여십시오. OFET에는 여러 접촉이 있기 때문에 1D 경우보다 더 많은 파일이 보입니다. 이는 각 접촉에 대해 JV 곡선이 생성되기 때문이며, 각 곡선은 해당 접촉을 통해 소자로 흐르거나 소자에서 나가는 전류를 나타냅니다. 생성되는 파일의 요약은 아래와 같습니다.

| 파일 이름 | 설명 |

|---|---|

| contact_iv0.dat | 접촉 0에 대한 전류 대 전압 곡선 |

| contact_iv1.dat | 접촉 1에 대한 전류 대 전압 곡선 |

| contact_iv2.dat | 접촉 2에 대한 전류 대 전압 곡선 |

| contact_jv0.dat | 접촉 0에 대한 전류 밀도 대 전압 곡선 |

| contact_jv1.dat | 접촉 1에 대한 전류 밀도 대 전압 곡선 |

| contact_jv2.dat | 접촉 2에 대한 전류 밀도 대 전압 곡선 |

| snapshots/ | 시뮬레이션 스냅샷 |

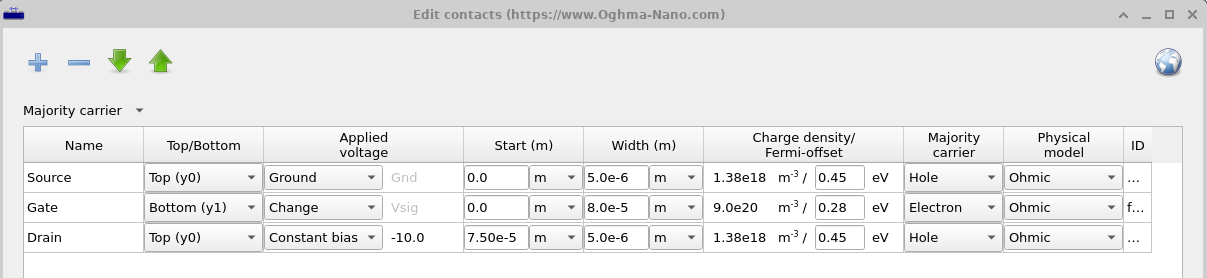

jv_contact_0.csv, jb_contact_1.csv, jb_contact_2.csv 파일을 더블 클릭하여 각 접촉의 곡선을 확인하십시오. OghmaNano의 접촉은 contact editor에 정의된 순서대로 0부터 N까지 레이블이 지정되므로(그림

?? 참조), 이 경우 Contact 0은 source, contact 1은 gate, contact 2는 drain이 됩니다. contact editor는 절 3.1.8에서 자세히 설명되었지만, 이것은 2D 시뮬레이션이므로 두 개의 추가 열이 나타납니다. 그것들은 start와 width입니다. 이들은 x축에서 접촉의 시작 위치와 x축에서의 접촉 폭을 정의합니다. source는 \(0~m\)에서 시작하여 \(5 \mu m\)까지 확장되고, drain은 \(75~\mu m\)에서 시작하여 \(5 \mu m\)까지 확장되며, gate는 \(0~m\)에서 시작하여 소자의 전체 폭인 \(80~ \mu m\)를 덮습니다. 또한 Applied Voltage 열 아래에서 source는 Ground로 표시되어 있는데, 이는 ground에 0V가 인가됨을 의미하고, gate는 change로 표시되어 JV editor에 정의된 전압 램프가 이 접촉에 인가됨을 의미하며, drain은 10V 전압의 constant bias로 표시되어 있으므로 이 접촉에는 일정한 10V가 인가됩니다. 따라서 우리는 source와 drain 사이에 일정한 전압을 인가하면서 gate 접촉을 스캔하고 있습니다.

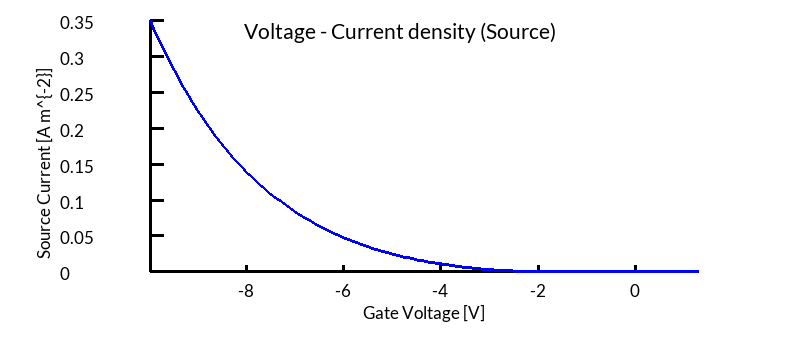

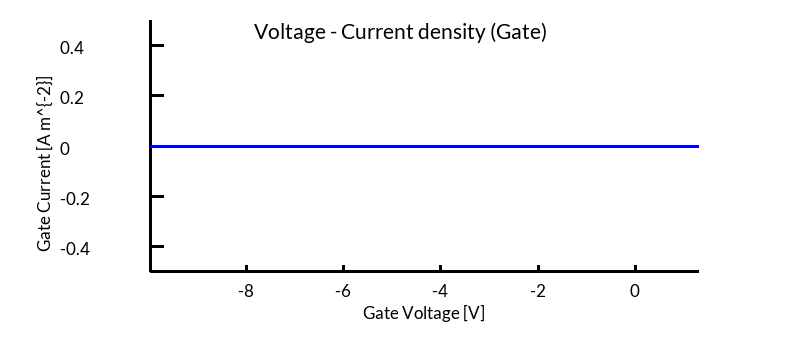

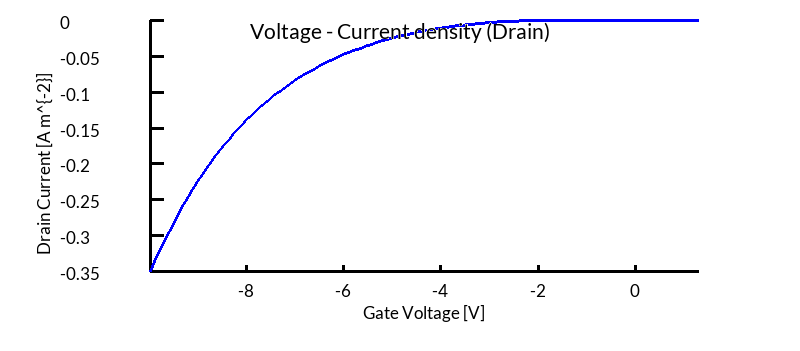

??, ?? 및 ??는 세 OFET 접촉 각각의 JV 곡선을 보여줍니다. ??와 ??를 보면 gate 전압이 더 음의 방향이 될수록 source와 drain의 전류도 더 음의 방향이 되는 것을 볼 수 있습니다. 우리는 채널이 전도하도록 정공을 끌어당기기 위해 음의 전압을 인가하고 있습니다. 또한 Gate에는 전류가 없음을 볼 수 있는데, 이는 전류가 dielectric에 의해 차단되기 때문입니다.

jv_contact0.csv - source)에 대한 JV 곡선입니다.

음의 부호는 이 단자를 통해 전류가 소자 밖으로 나감을 나타냅니다.

jv_contact1.csv - gate)에 대한 JV 곡선입니다.

gate는 절연되어 있으므로 전류는 0에 가깝게 유지됩니다.

jv_contact2.csv - drain)에 대한 JV 곡선입니다.

양의 전류는 전하가 소자로 주입됨을 나타냅니다.

👉 다음 단계: 이제 파트 B로 계속 진행하여 2D 및 3D에서 OFET 결과를 시각화하고, 전류 흐름, 전하 밀도, 소자 장을 더 자세히 탐색하는 방법을 배우십시오.